# Prototyping with Surface Mount Technology

Take your Design to the Market Well before Sunset

Ajith Narayanan

Zoid Labs

28 Feb 2019

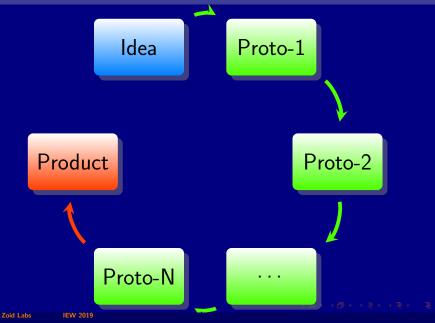

#### From Idea to Product

- Prototyping Strategies, Activities, Bottlenecks

- SMT PCB Assembly process & Tips

- Challenges in prototyping with SMT

- G Reducing cycle time with in-house assembly

- Streamlining with DFP (Design for Prototyping)

- Equipment and Process

- (8) Conclusion IEW 2019

- Prototyping Strategies, Activities, Bottlenecks

- SMT PCB Assembly process & Tips

- Challenges in prototyping with SMT

- 6 Reducing cycle time with in-house assembly

- Streamlining with DFP (Design for Prototyping)

- 7 Equipment and Process

- 8 Conclusion IEW 2019

- Prototyping Strategies, Activities, Bottlenecks

- 3 SMT PCB Assembly process & Tips

- Challenges in prototyping with SMT

- 6 Reducing cycle time with in-house assembly

- Streamlining with DFP (Design for Prototyping)

- Equipment and Process

- Conclusion IEW 2019

- Prototyping Strategies, Activities, Bottlenecks

- 3 SMT PCB Assembly process & Tips

- 4 Challenges in prototyping with SMT

- 6 Reducing cycle time with in-house assembly

- 6 Streamlining with DFP (Design for Prototyping)

- Equipment and Process

- 8 Conclusion IEW 2019

- Prototyping Strategies, Activities, Bottlenecks

- 3 SMT PCB Assembly process & Tips

- 4 Challenges in prototyping with SMT

- 5 Reducing cycle time with in-house assembly

- 6 Streamlining with DFP (Design for

- Prototyping)

- Equipment and Process

- (8) Conclusion

- Prototyping Strategies, Activities, Bottlenecks

- 3 SMT PCB Assembly process & Tips

- 4 Challenges in prototyping with SMT

- **5** Reducing cycle time with in-house assembly

- 6 Streamlining with DFP (Design for Prototyping)

- Equipment and Process

# 1 Introduction

- Prototyping Strategies, Activities, Bottlenecks

- 3 SMT PCB Assembly process & Tips

- 4 Challenges in prototyping with SMT

- **5** Reducing cycle time with in-house assembly

- 6 Streamlining with DFP (Design for Prototyping)

- 7 Equipment and Process

Conclusion

**IEW 2019**

# 1 Introduction

- Prototyping Strategies, Activities, Bottlenecks

- 3 SMT PCB Assembly process & Tips

- 4 Challenges in prototyping with SMT

- 5 Reducing cycle time with in-house assembly

- 6 Streamlining with DFP (Design for Prototyping)

- 7 Equipment and Process

- 8 Conclusion

Zoid Labs

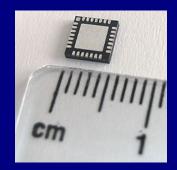

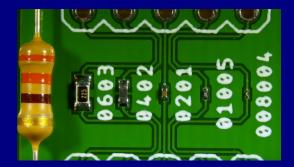

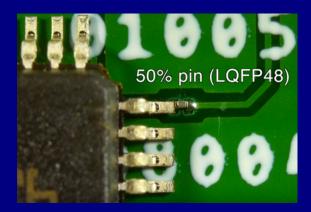

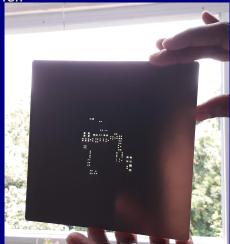

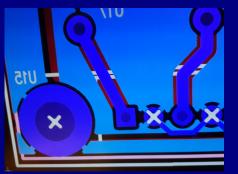

# SMT chip

Zoid Labs IEW 2019

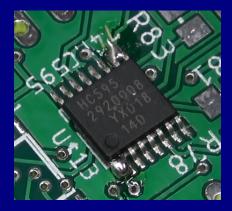

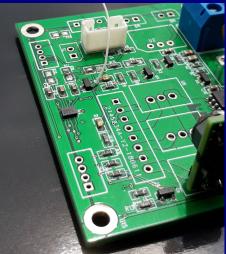

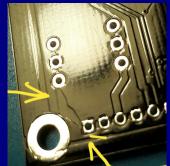

# SMT board

<ロ> < 団> < 団> < 豆> < 豆> < 豆> < 豆 < りへの 13

Zoid Labs IEW 2019

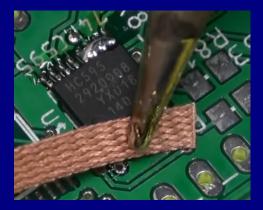

SMT Mayhem

More Mayhem

16

0201 =0.6 x 0.3 mm, 20 x 10 mil, 0.02 x 0.01"

008004 8x4 mil = 0.2 x 0.1 mm

#### Section 2

18

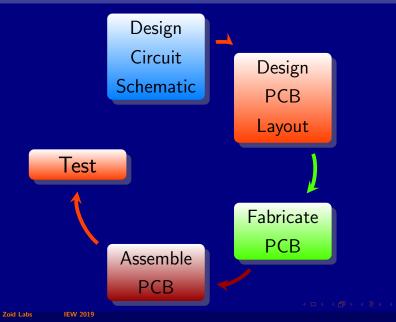

Prototyping: Strategies, Activities, Bottlenecks

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly ightarrow Full assembly

- Big Bang approach

Build and test completely assembled PCB Typically for product-intent PCBs More common towards later stages of prototyping

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly  $\rightarrow$  Full assembly

- Big Bang approach

Build and test completely assembled PCB Typically for product-intent PCBs More common towards later stages of prototyping

20

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly  $\rightarrow$  Full assembly

- Big Bang approach

Build and test completely assembled PCB Typically for product-intent PCBs More common towards later stages of prototyping

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly ightarrow Full assembly

- Big Bang approach

Build and test completely assembled PCB Typically for product-intent PCBs More common towards later stages of prototyping

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly ightarrow Full assembly

- Big Bang approach

- Build and test completely assembled PCB

- Typically for product-intent PCBs

- More common towards later stages of prototyping

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly ightarrow Full assembly

- Big Bang approach

- Build and test completely assembled PCB

- Typically for product-intent PCBs

- More common towards later stages of prototyping

# • Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly ightarrow Full assembly

- Big Bang approach

- Build and test completely assembled PCB

- Typically for product-intent PCBs

- More common towards later stages of prototyping

# Divide and Conquer approach

- E.g. Build and test a sub-circuit

- More common towards early stages of prototyping

- Partial assembly → Full assembly

- Big Bang approach

- Build and test completely assembled PCB

- Typically for product-intent PCBs

- More common towards later stages of prototyping

#### **Activities in Prototyping**

# Activities (in successive steps)

Zoid Labs

28

# • Say 5 iterations

- If a typ. iteration takes 1 day  $\Rightarrow$  5 days

- If it takes 4 weeks  $\Rightarrow$  5 months!

- $\Rightarrow$  Critical to have fast turn-around

- $\Rightarrow$  Cycle time can make it or break it!

30

- Say 5 iterations

- If a typ. iteration takes 1 day  $\Rightarrow$  5 days

- If it takes 4 weeks  $\Rightarrow$  5 months!

- $\Rightarrow$  Critical to have fast turn-around

- $\Rightarrow$  Cycle time can make it or break it!

- Say 5 iterations

- If a typ. iteration takes 1 day  $\Rightarrow$  5 days

- If it takes 4 weeks  $\Rightarrow$  5 months!

- $\Rightarrow$  Critical to have fast turn-around

- $\Rightarrow$  Cycle time can make it or break it!

- Say 5 iterations

- If a typ. iteration takes 1 day  $\Rightarrow$  5 days

- If it takes 4 weeks  $\Rightarrow$  5 months!

- $\Rightarrow$  Critical to have fast turn-around

- $\Rightarrow$  Cycle time can make it or break it!

- Say 5 iterations

- If a typ. iteration takes 1 day  $\Rightarrow$  5 days

- If it takes 4 weeks  $\Rightarrow$  5 months!

- $\Rightarrow$  Critical to have fast turn-around

- $\Rightarrow$  Cycle time can make it or break it!

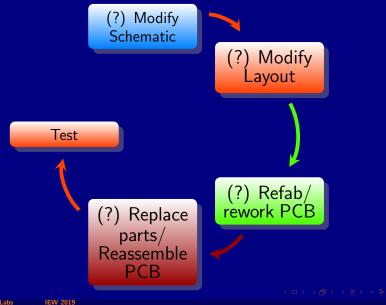

#### **Bottlenecks**

#### **Bottlenecks**

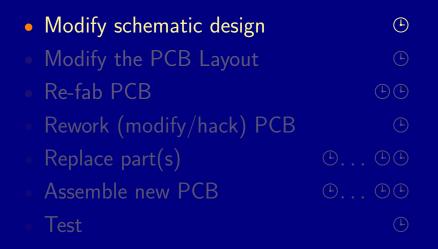

# Bottlenecks

|   | Modify schematic design  | Ŀ    |

|---|--------------------------|------|

|   | Modify the PCB Layout    | Ŀ    |

| • | Re-fab PCB               | ĿĿ   |

|   | Rework (modify/hack) PCB | Ŀ    |

|   | Replace part(s)          | ╚ ╚╚ |

|   | Assemble new PCB         | ╚ ╚╚ |

|   | Test                     | Ŀ    |

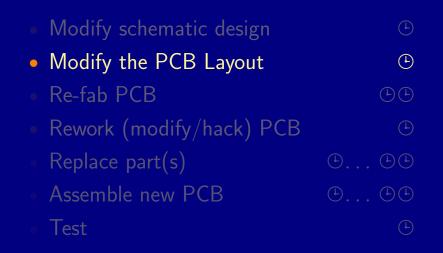

|   | Modify schematic design  | Ŀ                         |

|---|--------------------------|---------------------------|

|   | Modify the PCB Layout    | Ŀ                         |

|   | Re-fab PCB               | ( <b>b</b> ) ( <b>b</b> ) |

| • | Rework (modify/hack) PCB | Ŀ                         |

|   | Replace part(s)          | ₾ ₾₽                      |

|   | Assemble new PCB         | ₾ ₾₽                      |

|   | Test                     | Ŀ                         |

|   | Modify schematic design  | Ŀ           |

|---|--------------------------|-------------|

|   | Modify the PCB Layout    | Ŀ           |

|   | Re-fab PCB               | (,,,,,,,,,, |

|   | Rework (modify/hack) PCB | Ŀ           |

| • | Replace part(s)          | ⊕ ⊕⊕        |

|   | Assemble new PCB         | ₾ ₾₽        |

|   | Test                     | Ŀ           |

|   | Modify schematic design  |                  |

|---|--------------------------|------------------|

|   | Modify the PCB Layout    | ( <del>L</del> ) |

|   | Re-fab PCB               | (L) (L)          |

|   | Rework (modify/hack) PCB | ( <b>L</b> )     |

|   | Replace part(s)          | Ŀ ĿĿ             |

| • | Assemble new PCB         | ₾ ₾₾             |

|   | Test                     | ( <b>L</b> )     |

|   | Modify schematic design  |      |

|---|--------------------------|------|

|   | Modify the PCB Layout    | Ŀ    |

|   | Re-fab PCB               |      |

|   | Rework (modify/hack) PCB | Ŀ    |

|   | Replace part(s)          | ╚ ╚╚ |

|   | Assemble new PCB         | ╚ ╚╚ |

| • | Test                     | Ŀ    |

41

# SMT Assembly Process & Process Tips

Zoid Labs IEW 2019

#### SMT PCB Assembly – PCBs, Stencils

#### Unframed or "cut" stencil

#### SMT PCB Assembly – PCBs, Stencils

#### PCB after placing and reflow

#### SMT PCB Assembly – PCBs, Stencils

#### Assembled PCB, with minor rework

- Lay the PCB right side up, for stencilling

- Overlay with stencil, adjust until registration is good

- Apply solder paste, squeegee through

- Examine solder paste coverage

- Remove stencil without smudging

- Lay the PCB right side up, for stencilling

- Overlay with stencil, adjust until registration is good

- Apply solder paste, squeegee through

- Examine solder paste coverage

- Remove stencil without smudging

- Lay the PCB right side up, for stencilling

- Overlay with stencil, adjust until registration is good

- Apply solder paste, squeegee through

- Examine solder paste coverage

- Remove stencil without smudging

- Lay the PCB right side up, for stencilling

- Overlay with stencil, adjust until registration is good

- Apply solder paste, squeegee through

- Examine solder paste coverage

- Remove stencil without smudging

- Lay the PCB right side up, for stencilling

- Overlay with stencil, adjust until registration is good

- Apply solder paste, squeegee through

- Examine solder paste coverage

- Remove stencil without smudging

# On their pads, get set...Go!Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven

Run appropriate cooking profile

Remove, Inspect, Re-heat if necessary

- Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven

Run appropriate cooking profile

Remove, Inspect, Re-heat if necessary

- Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven

Run appropriate cooking profile

Remove, Inspect, Re-heat if necessary

- Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven Run appropriate cooking profile

Remove, Inspect, Re-heat if necessary

- Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven Run appropriate cooking profile

Remove, Inspect, Re-heat if necessary

- Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven Run appropriate cooking profile

Remove, Inspect, Re-heat if necessary

- Pick and place components on wet PCB

- Ensure parts are correct

- Ensure polarity/orientation

- Don't let solder paste dry up

- If doing manually with tweezers, don't let parts fly!

- Put loaded PCB into oven Run appropriate cooking profile

- Remove, Inspect, Re-heat if necessary

#### SMT PCB Assembly Process (3/3)

57

# Finishing up! Brush & clean with Iso-Propyl Alcohol (IPA) Test for power shorts ...Go on to power up test

#### SMT PCB Assembly Process (3/3)

58

#### Finishing up!

- Brush & clean with Iso-Propyl Alcohol (IPA)

- Test for power shorts

- ... Go on to power up test

#### SMT PCB Assembly Process (3/3)

# Finishing up!

- Brush & clean with Iso-Propyl Alcohol (IPA)

- Test for power shorts

- ... Go on to power up test

- Usually outsourcing is good.

- \$ and 🕑 encourage outsourcing

- Standard materials and spec, specialized job, chemical hazards, equipment/skills.

- But inspect results carefully.

- "100% tested" may not be so!

- "Cut stencils" are cheap and good

- Usually outsourcing is good.

- \$ and 🕑 encourage outsourcing

- Standard materials and spec, specialized job, chemical hazards, equipment/skills.

- But inspect results carefully.

"100% tested" may not be so!

- "Cut stencils" are cheap and good

$(\dot{z})$

- Usually outsourcing is good.

- \$ and  $\oplus$  encourage outsourcing

- Standard materials and spec, specialized job, chemical hazards, equipment/skills.

- But inspect results carefully.

- "100% tested" may not be so!

- "Cut stencils" are cheap and good

$(\dot{z})$

- Usually outsourcing is good.

- \$ and  $\oplus$  encourage outsourcing

- Standard materials and spec, specialized job, chemical hazards, equipment/skills.

- But inspect results carefully.

- "100% tested" may not be so!

- "Cut stencils" are cheap and good

#### Paste and Cooking tips

### Pasta!

- Use good "Lead Free" paste.

Right Type (grain size e.g. Type 3, Type 4)

- Store paste in fridge

Let it warm up before applying

#### Paste and Cooking tips

65

## Pasta!

- Use good "Lead Free" paste.

Right Type (grain size e.g. Type 3, Type 4)

- Store paste in fridge Let it warm up before applying

66

# Challenges in Prototyping

Zoid Labs IEW 2019

• Design/Layout issues:

444©**\$\$\$**

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

- Design/Layout issues: 444©\$\$\$

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

- Design/Layout issues: 444©\$\$\$

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

#### Design/Layout issues: 444©\$\$\$

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

#### Design/Layout issues: 444©\$\$\$

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

#### Design/Layout issues: 444©\$\$\$

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

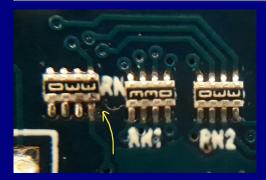

## Typical Challenges/Errors/Mistakes

## Design/Layout issues: 444©\$\$\$

- Sufficient test access?

- Sufficient rework/repair access?

- Components used as per design?

- Correct placement done? (C12 in place of R12?)

- Correct polarity / orientation?

- Correctly rated part used?

#### Some actual errors (mistakes)

## *Problem*: Board worked for 3 days, then stopped.

*Problem*: Board worked for 3 days, then stopped.

## Culprit: Rating!

PCB with many decoupler caps (0.1  $\mu$ F 10V) Had a charge pump using one 0.1  $\mu$ F 50V. Assembly used the same capacitor for all. Cap failed (dielectric punch through).

#### A fab error

#### Power board with fab error, a $V_{out}$ shorted to GND

## A Reflow soldering slip-up

77

#### Soldering defect revealed by careful inspection

78

# Reducing Cycle Time with In-house Assembly

Zoid Labs IEW 2019

Assembly error: rework 1 or entire batch

PCB fabrication error: re-fab PCB, ...

Schematic error: Re layout, re-fab, ...

Fix and repeat tests

Assembly error: rework 1 or entire batch

PCB fabrication error: re-fab PCB, ...

Schematic error: Re layout, re-fab, ...

Fix and repeat tests

81

- Assembly error: rework 1 or entire batchPCB fabrication error: re-fab PCB, ...

- Schematic error: Re layout, re-fab, ...

Fix and repeat tests

82

Assembly error: rework 1 or entire batch

PCB fabrication error: re-fab PCB, ...

Schematic error: Re layout, re-fab, ...

Fix and repeat tests

#### Hardware/Software Co-Design

#### GIOVANNI DE MICHELI, FELLOW, IEEE, AND RAJESH K. GUPTA, MEMBER, IEEE

#### Invited Paper

Most electronic systems, whether self-contained or embedded, have a predominant digital component consisting of a hardware platform which executes software application programs. Hardware/software co-design means meeting system-level objectives by exploiting the synergism of hardware and software through their concurrent design. Co-design problems have different flavors according to the application domain, implementation technology and design methodology.

Digital hardware design has increasingly more similarities to software design. Hardware circuits are often described using modeling or programming languages, and they are validated and implemented by executing software programs, which are sometimes Moreover, the implementation of electronic systems and subsystems shows often a predominant digital component.

We focus in this paper on the digital component of electronic systems, and refer to them as (digital) systems for brevity. The majority of such systems are programmable, and thus consist of hardware and software components. The value of a system can be measured by some objectives that are specific to its application domain (e.g., performance, design, and manufacturing cost, and ease of programmabil-

ity) and it depends on both the hardware and the software

(Micheli & Gupta, Proc. IEEE, Vol.85, No.3, March 1997)

- to test 1-channel in a 6-channel board

- for sub-circuit level prototyping

- for minimum h/w to get s/w dev started

- to skip some expensive parts (when not immediately needed), e.g. connectors, some peripherals

- to test 1-channel in a 6-channel board

- for sub-circuit level prototyping

- for minimum h/w to get s/w dev started

- to skip some expensive parts (when not immediately needed), e.g. connectors, some peripherals

- to test 1-channel in a 6-channel board

- for sub-circuit level prototyping

- for minimum h/w to get s/w dev started

- to skip some expensive parts (when not immediately needed), e.g. connectors, some peripherals

- to test 1-channel in a 6-channel board

- for sub-circuit level prototyping

- for minimum h/w to get s/w dev started

- to skip some expensive parts (when not immediately needed), e.g. connectors, some peripherals

- Speeds up initial bring-up of proto and test boards

- Allows Hw/Sw Co-Design during proto

- Reduces unpredictability arising from external factors

- Reduces overall product development time & cost

- Speeds up initial bring-up of proto and test boards

- Allows Hw/Sw Co-Design during proto

- Reduces unpredictability arising from external factors

- Reduces overall product development time & cost

- Speeds up initial bring-up of proto and test boards

- Allows Hw/Sw Co-Design during proto

- Reduces unpredictability arising from external factors

- Reduces overall product development time & cost

- Speeds up initial bring-up of proto and test boards

- Allows Hw/Sw Co-Design during proto

- Reduces unpredictability arising from external factors

- Reduces overall product development time & cost

- Speeds up initial bring-up of proto and test boards

- Allows Hw/Sw Co-Design during proto

- Reduces unpredictability arising from external factors

- Reduces overall product development time & cost

- Speeds up initial bring-up of proto and test boards

- Allows Hw/Sw Co-Design during proto

- Reduces unpredictability arising from external factors

- Reduces overall product development time & cost

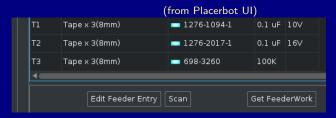

## Assembly – Pick & Place

#### Assembly – on the desktop

#### Goals set for Zoid Labs' Placerbot:

$\checkmark$  To fit desktop  $\checkmark$  Be portable  $\checkmark$  Handle typical parts ✓ Accuracy  $\checkmark$  Repeatability  $\checkmark$  Handle cut tapes  $\checkmark$  Also feed from tray  $\checkmark$  Be flexible  $\checkmark$  Easy to use

Placerbot

- To leverage Partial Assembly

- To reduce cycle time per iteration

- To reduce overall dev time and cost

- To reduce errors (e.g. below)

- To leverage Partial Assembly

- To reduce cycle time per iteration

- To reduce overall dev time and cost

- To reduce errors (e.g. below)

- To leverage Partial Assembly

- To reduce cycle time per iteration

- To reduce overall dev time and cost

- To reduce errors (e.g. below)

- To leverage Partial Assembly

- To reduce cycle time per iteration

- To reduce overall dev time and cost

- To reduce errors (e.g. below)

- To leverage Partial Assembly

- To reduce cycle time per iteration

- To reduce overall dev time and cost

- To reduce errors (e.g. below)

Increased visibility / Early visibility into all aspects of design e.g. Mechanical issues, Thermal design Prepares for DFM and productization Total Control over Intellectual Property Design and BOM optimization

- Increased visibility / Early visibility into all aspects of design e.g. Mechanical issues, Thermal design

- Prepares for DFM and productization

- Total Control over Intellectual Property

- Design and BOM optimization

- Increased visibility / Early visibility into all aspects of design e.g. Mechanical issues, Thermal design

- Prepares for DFM and productization

- Total Control over Intellectual Property

- Design and BOM optimization

- Increased visibility / Early visibility into all aspects of design e.g. Mechanical issues, Thermal design

- Prepares for DFM and productization

- Total Control over Intellectual Property

- Design and BOM optimization

105

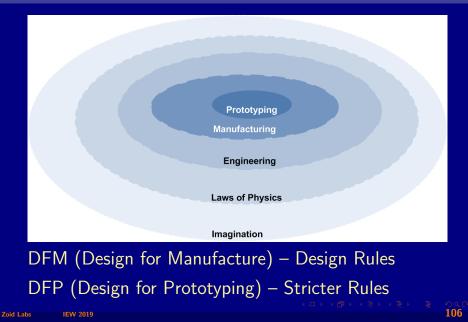

Streamlining with DFP (Design for Prototyping)

### **Basic Approach**

# Some DFP Tips (1/3) (As practised at Zoid Labs)

# General

Provision fuses. (Final product may or may not include these)

Use 0R's (0Ω) or fuses to isolate power paths.

Have all DFP additions (0Ω etc) with 0805 footprints (smaller size ⇒ ☺ ☺ for tweezers)

# Some DFP Tips (1/3) (As practised at Zoid Labs)

# General

Provision fuses. (Final product may or may not include these)

Use 0R's (0Ω) or fuses to isolate power paths.

Have all DFP additions (0Ω etc) with 0805 footprints (smaller size ⇒ ☺ ☺ for tweezers)

# Some DFP Tips (1/3) (As practised at Zoid Labs)

# General

- Provision fuses.

(Final product may or may not include these)

- Use 0R's (0Ω) or fuses to isolate power paths.

- Have all DFP additions (0Ω etc) with 0805 footprints

(smaller size  $\Rightarrow \odot \odot$  for tweezers)

# Testability

- Add testpoints liberally

- say  $0.5 \times 0.5$ mm pad for occasional probing

- Where needed to hook up a probe often, add a thru-hole pin pad.

- Provision configuration 0R's

- For intercepting signals

- To provide alternate paths (mux/demuxing)

- Strapping options

- (e.g. mode inputs, I2C addresses)

- Allow space for test/probe access

# Testability

- Add testpoints liberally

- say  $0.5 \times 0.5$ mm pad for occasional probing

- Where needed to hook up a probe often, add a thru-hole pin pad.

- Provision configuration 0R's

- For intercepting signals

- To provide alternate paths (mux/demuxing)

- Strapping options

- (e.g. mode inputs, I2C addresses)

- Allow space for test/probe access

# Testability

- Add testpoints liberally

- say  $0.5 \times 0.5$ mm pad for occasional probing

- Where needed to hook up a probe often, add a thru-hole pin pad.

- Provision configuration 0R's

- For intercepting signals

- To provide alternate paths (mux/demuxing)

- Strapping options

- (e.g. mode inputs, I2C addresses)

- Allow space for test/probe access

- Use rounded pads in footprints

- For small passives

- Less likely to 'tombstone'

- Better for IC's too

- Careful with big thermal pads (belly pads)!

- Prefer non-BGA packages if possible

- More leeway with solder reflow profile

- Include fiducial marks (local,global)

- Include fiducial marks in Stencil for easy registration visually

- Undersize stencil openings slightly

- Use rounded pads in footprints

- For small passives

- Less likely to 'tombstone'

- Better for IC's too

- Careful with big thermal pads (belly pads)!

- Prefer non-BGA packages if possible

- More leeway with solder reflow profile

- Include fiducial marks (local,global)

- Include fiducial marks in Stencil for easy registration visually

- Undersize stencil openings slightly

- Use rounded pads in footprints

- For small passives

- Less likely to 'tombstone'

- Better for IC's too

- Careful with big thermal pads (belly pads)!

- Prefer non-BGA packages if possible

- More leeway with solder reflow profile

- Include fiducial marks (local,global)

- Include fiducial marks in Stencil for easy registration visually

- Undersize stencil openings slightly

- Use rounded pads in footprints

- For small passives

- Less likely to 'tombstone'

- Better for IC's too

- Careful with big thermal pads (belly pads)!

- Prefer non-BGA packages if possible

- More leeway with solder reflow profile

- Include fiducial marks (local,global)

- Include fiducial marks in Stencil for easy registration visually

- Undersize stencil openings slightly

- Use rounded pads in footprints

- For small passives

- Less likely to 'tombstone'

- Better for IC's too

- Careful with big thermal pads (belly pads)!

- Prefer non-BGA packages if possible

- More leeway with solder reflow profile

- Include fiducial marks (local,global)

- Include fiducial marks in Stencil for easy registration visually

- Undersize stencil openings slightly

- Use rounded pads in footprints

- For small passives

- Less likely to 'tombstone'

- Better for IC's too

- Careful with big thermal pads (belly pads)!

- Prefer non-BGA packages if possible

- More leeway with solder reflow profile

- Include fiducial marks (local,global)

- Include fiducial marks in Stencil for easy registration visually

- Undersize stencil openings slightly

119

# What Equipment? Process support etc

Zoid Labs IEW 2019

- Stencilling machines??

- Inspection capability

- 🔹 Auto Pick and Place: 🗸

Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up Easier to repeat the run (than manual) Should do 0402, cut tape, fine pitch ICs

PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up Easier to repeat the run (than manual) Should do 0402, cut tape, fine pitch ICs

PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up Easier to repeat the run (than manual) Should do 0402, cut tape, fine pitch ICs

PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity,

orientation. Faster than manual process;

else paste may dry up

- Easier to repeat the run (than manual)

- Should do 0402, cut tape, fine pitch ICs

- PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up

- Easier to repeat the run (than manual)

- Should do 0402, cut tape, fine pitch ICs

- PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up

- Easier to repeat the run (than manual)

Should do 0402, cut tape, fine pitch ICs

- PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up

- Easier to repeat the run (than manual)

- Should do 0402, cut tape, fine pitch ICs

- PCB Oven: √

Verify temp. profiles for Pb & Pb-free Verify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up

- Easier to repeat the run (than manual)

- Should do 0402, cut tape, fine pitch ICs

- PCB Oven: ✓

- Verify temp. profiles for Pb & Pb-freeVerify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up

- Easier to repeat the run (than manual)

- Should do 0402, cut tape, fine pitch ICs

### ● PCB Oven: ✓

Verify temp. profiles for Pb & Pb-freeVerify heat distribution

- Stencilling machines??

- Inspection capability  $\checkmark$

- Auto Pick and Place: √

- Ensures correct parts, polarity, orientation. Faster than manual process; else paste may dry up

- Easier to repeat the run (than manual)

- Should do 0402, cut tape, fine pitch ICs

# ● PCB Oven: ✓

- Verify temp. profiles for Pb & Pb-free

- Verify heat distribution

- Managing components: e.g. cut tapes

- Managing part numbers

- HPN House Part No, MPN Mfr Part No, DPN – Distributor Part No, DPN2 –Alternate Distributer Part No. ... etc and equivalences between these part numbers.

#### Conclusions

# **1** SMT Prototyping can be challenging

- To cut cycle-time/cost, have in-house assembling capability

- Ise DFP (Design For Prototyping) guidelines

- Appropriate Equipment and Process

Thank You!

- **1** SMT Prototyping can be challenging

- 2 To cut cycle-time/cost, have in-house assembling capability

- Ise DFP (Design For Prototyping) guidelines

- Appropriate Equipment and Process

Thank You!

- **1** SMT Prototyping can be challenging

- 2 To cut cycle-time/cost, have in-house assembling capability

- 3 Use DFP (Design For Prototyping) guidelines

- Appropriate Equipment and Process

Thank You!

Zoid Labs

- **1** SMT Prototyping can be challenging

- 2 To cut cycle-time/cost, have in-house assembling capability

- 3 Use DFP (Design For Prototyping) guidelines

- Appropriate Equipment and Process

ajith@zoidlabs.com

Thank You!

- **1** SMT Prototyping can be challenging

- 2 To cut cycle-time/cost, have in-house assembling capability

- 3 Use DFP (Design For Prototyping) guidelines

- Appropriate Equipment and Process

ajith@zoidlabs.com

Thank You!

- **1** SMT Prototyping can be challenging

- 2 To cut cycle-time/cost, have in-house assembling capability

- 3 Use DFP (Design For Prototyping) guidelines

- Appropriate Equipment and Process

Thank You!